先端テクノロジ

F-ALCS

(エフアルシス)技術

FICTが提供する「F-ALCS(エフアルシス)」は、高速信号伝送を可能にする画期的なめっきレスビア形成プリント基板技術です。

F-ALCS(エフアルシス)に

F-ALCS(エフアルシス)に

ついて

FICTが提供する「F-ALCS(エフアルシス)」は、高速信号伝送を可能にする画期的なめっきレスビア形成プリント基板技術です。超高多層、高密度な配線の実現により、配線収容能力を飛躍的に向上させました。全層IVH(Interstitial Via Hole)構造は、ペースト充填と金属間結合により形成し高い接続信頼性を可能にしています。

情報技術の劇的な進化を背景にして、クラウドコンピューティングやAI(人工知能)が当たり前になり、それらの基盤となるデータセンターのニーズが急速に拡大しました。また、デジタル社会における高速で大容量のデータ通信を支える5Gや、光通信等の社会インフラを担う情報通信機器の需要が益々増加しています。

これらの高度なデータ処理装置に採用されるプリント基板には、「高多層・高密度・低伝送ロス」を有した構造が必要とされています。F-ALCSが持つ設計自由度の高い革新的なプリント基板技術で、情報化社会におけるお客様の様々な要望にお応えします。

製品紹介動画 F-ALCS

F-ALCS(エフアルシス)の

F-ALCS(エフアルシス)の

4つの特徴

"F-ALCS"技術の4つの特徴をご紹介します。

特徴 01

プリント基板設計の自由度が高い

F-ALCSは、層間接続で使用するビア(導通穴)を、各層で必要な部分にのみ配置でき、ビアパッドも小径化されているため、部品を自由に配置できます。ビアや部品配置などの制約から解放されることで、配線に有効なエリアが飛躍的に拡大します。最大72層の全層IVH構造に対応。140層レベルの配線が可能です。

ポイント:実装エリアが拡大

貫通基板や一般IVH基板(貼合わせ基板)では、ドリルで上下に貫通加工したスルーホールが配置されるため、基板表面に穴のあいた部分が発生し、部品を実装するエリアが制限されます。

一方、F-ALCSは各層毎に必要なビア(導通穴)をあけ、導電性ペーストを充填、その後全層一括積層を行うことによって、必要な部分に必要な分だけビアを配置できます。

その結果、これまでスルーホールで部品配置が出来なかった場所を実装エリアとして使えるようになります。

特徴 02

伝送ロス、反射ロスの低減で高速伝送特性をアップ

F-ALCSは全層IVH構造により、ビア部分に高速信号伝送の阻害要因となるスタブが発生しません。リターンロスを低減することで、高周波まで良好な伝送特性が得られ、より高速な信号伝送が期待できるのです。

下の図では、従来の貫通基板とF-ALCSにおいて、構造の違いによる伝送特性を比較しました。

F-ALCSは、全層IVH構造の実現により不要なビアスタブ(オープンスタブ)が無くなることで、伝送ロス、反射ロスが低減し、高周波まで良好な伝送特性が得られます。だからこそ、高性能AIサーバや5G通信機器向けなど、プリント基板に要求される高周波動作に対応できるのです。

F-ALCS構造による伝送特性の改善効果

~貫通PTH構造とF-ALCS構造比較~

特徴 03

納期短縮を実現!「一括積層工法」により工程数を半減

貫通基板や一般IVH基板(貼合わせ基板)の製造プロセスは、内層の配線形成から始まり表面層形成まで、10工程が一般的です。 それに対してF-ALCSのプロセスは、内層を並行して配線形成し、レーザによる穴あけと導電ペーストの印刷でIVHを形成します。その後、一括積層を行うことで全てのビア接続が完了します。従来の貫通基板や貼合わせ基板と異なり、プロセス自体が5工程に半減され、納期短縮につながります。

プロセスステップ数の比較

自由度の高いストレスフリーな設計環境と、製造工程数の半減により、設計から製造まで工程全体の納期短縮を実現します。

特徴 04

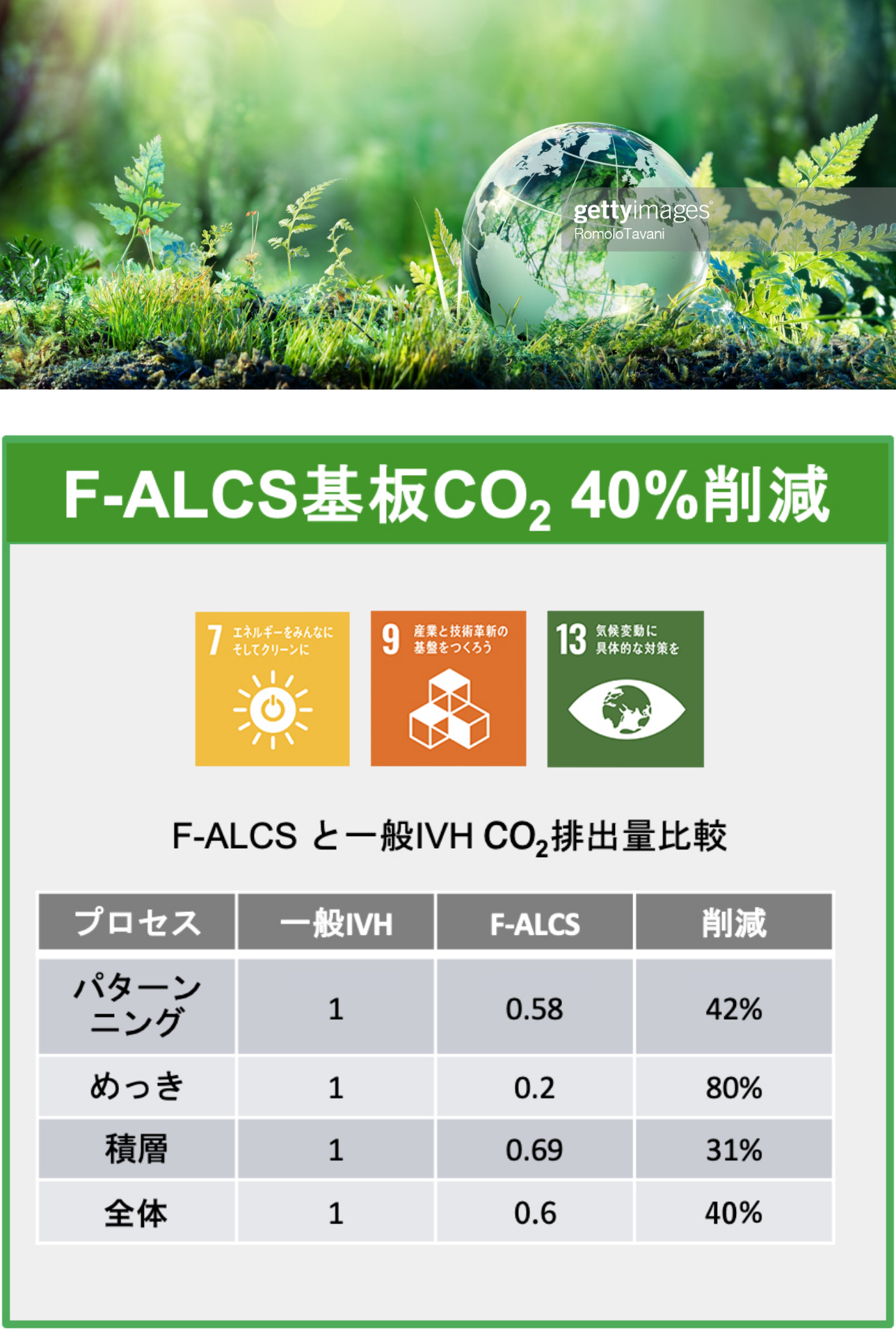

めっき不要でCO₂を40%削減、環境に配慮

ビアの接続をめっき工程から導電ペースト印刷工程に置き換えたことにより、めっき液などの廃液処理が不要となります。また、ランニングコスト(水・電気・処理時間)が抑えられ、製造過程における二酸化炭素排出量を約40%削減します。

環境に配慮したF-ALCS製造プロセスにより、環境に優しい製品の提供に尽力しています。

お客様の声

お客様の声

F-ALCSを使用されたお客様の声をご紹介します。

-

高密度配線で最新の半導体にも対応

半導体の集積度が上がって、ウエハーの電気試験用プリント基板の配線数が増えており、従来のプリント基板設計では配線密度に限界が来て困っていました。

F-ALCSを使うことで配線密度を上げることができ、

最新の半導体にも対応できました。 -

開発期間の短縮で短納期を実現

今までの高多層、高密度プリント基板の調達では、取引先の要求納期に対応できず、いつも調整が必要でした。

F-ALCSは、設計や基板製造の期間が短縮され、

お客様のスケジュールに合わせた対応が可能になりました。 -

スタブレスで高速化を実現

ネットワークの高速化に合わせて、プリント基板上の信号伝送も高速化の必要がありましたが、ビアのスタブの軽減がネックでした。

F-ALCSは全層ビルドアップ構造なので、

スタブを気にする必要が無く、設計が容易になりました。

適用事例

適用事例

事例 01

ICTインフラ製品向け高密度基板(F-ALCS)

ハイエンドサーバ、5Gインフラ、HPC向け基板は大型化により大量な配線が必要とされています。

そのため、全層IVH製法のF-ALCS技術を適用することで飛躍的に配線収容能力が向上します。さらに、一括積層方式のため短納期での製造が可能です。

仕様

| 基板サイズ | φ480mm |

|---|---|

| 層数 | 76層 |

| Pad ピッチ | 495µm |

| Pad 径 | φ300µm |

| Via 径 | φ180µm |

| 絶縁層厚 | 100µm |

| 板厚 | 7.4mmt |

構造

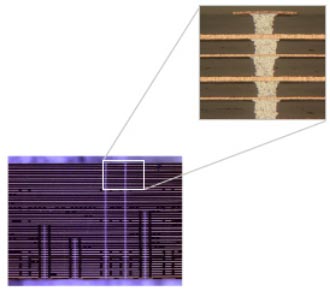

<X-section>

事例 02

半導体テスト装置用プローブカード(F-ALCS+ビルドアップ)

プローブカードの多ピン化や狭ピッチ化により、プローブカードに収容が必要なワイヤー数が膨大となり、片側16段ビルドアップを超える配線層数が必要となります。

そこで、コア部にF-ALCS技術を採用することで、コア部の配線収容能力を飛躍的に向上させることができ、その結果ビルドアップ層数を抑制して全体の層数を削減できます。

仕様

<F-ALCS Core部>

| 基板サイズ | □150mm |

|---|---|

| 層数 | 28層 |

| Pad ピッチ | 280µm |

| Pad 径 | φ170µm |

| Via 径 | φ110µm |

| 絶縁層厚 | 60µm |

構造

<X-section>

関連技術

関連技術

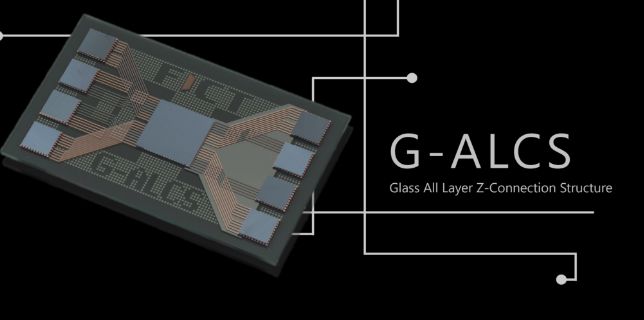

F-ALCS技術を応用した次世代半導体パッケージ向けガラスコア基板

G-ALCS (Glass All Layer Z-Connection Structure)です。

製品紹介動画 G-ALCS